”IC验证 静态时序分析“ 的搜索结果

ASIC芯片设计静态时序分析(STA)验证综合编程规范IC设计与方法等文档资料: ASIC Guide from Atmel.pdf asic_design_guide.pdf ASIC中的异步时序设计.doc ASIC设计教程.pdf asynchronous signals in a synchronous ...

数字集成电路静态时序分析基础.pdf

静态时序分析有两种模式:PBA(Path Based Analysis)和GBA(Graph Based Analysis),PBA是基于路径的分析模式而GBA则是基于图的分析模式。在Design Compiler中,时序分析是使用GBA模式;而在PrimeTime中,既可以使用...

静态时序分析实践.rar

标签: STA

AHB-SRAMC和FIFO的设计与验证.rar clock skew.rar IC攻城狮求职宝典.rar linux basic.rar Linux EDA虚拟机 - 个人学习IC设计.rar Perl语言在芯片设计中的应用.rar SoC芯片设计技能专题.rar SystemVerilog Assertion...

且运行速度很快、占用内存较少,不仅可以对芯片设计进行全面的时序功能检查,而且还可利用时序分析的结果来优化设计,因此静态时序分析已经越来越多地被用到数字集成电路设计的验证中。 缺点:但是它只能用于分析...

静态时序分析(Static Timing Analysis, STA),或称静态时序验证,是电子工程中,对数字电路的时序进行计算、预计的工作流程,该流程不需要通过输入激励的方式进行仿真。它是IC/FPGA设计中至关重要的一环,也是笔试...

介绍了数字集成电路设计中静态时序分析和形式验证的一般方法和流程

静态时序分析(简称STA)是用来验证数字设计时序的技术之一,另外一种验证时序的方法是时序仿真,时序仿真可以同时验证功能和时序。“时序分析”这个术语就是用来指代“静态时序分析“或”时序仿真“这两种方法之一...

静态时序分析:是分析,调试并确认一个门级系统设计时序性能的方法。检验门级电路的最大延迟,以保证在指定的频率下,能够满足建立时间的要求;检验门级电路的最小延迟,以保证在指定的频率下,能够满足保持时间的...

静态时序分析(英语:Static Timing Analysis, STA),或称静态时序验证,是电子工程中,对数字电路的时序进行计算、预计的工作流程,该流程不需要通过输入激励的方式进行仿真。

静态时序分析(STA)是一种通过检查所有可能的路径是否存在时序违规来验证设计时序性能的方法。 STA将设计分解为时序路径,计算沿每个路径的信号传播延迟,并检查设计内部和输入/输出接口处时序约束的违反情况。

(1) 静态时序分析是一种验证数字集成电路时序是否合格的验证方法; (2) 静态时序分析的前提是同步逻辑设计(重要!),不能分析异步电路; (3) 静态时序分析工具计算路径延迟的总和,并比较相对于预定义时钟的...

静态时序分析是一种常用的IC设计验证方法,用于评估电路的时序性能是否满足要求。在静态时序分析中,首先建立电路的时序模型,然后采用时序分析工具进行分析。时序模型中包括时钟周期、输出延迟、输入到输出延迟等...

其次,电路的时序是否满足,通过STA(静态时序分析)得到。两种验证手段相辅相成,确保验证工作高效、可靠地完成。时序分析的主要作用是查看FPGA内部逻辑和布线的延时,确保其是否满足设计者的...

(2)一个器件的性能由构成设计单元的延迟决定,它可以通过静态时序分析(Static Timing Analysis,STA)验证。 (3)在STA中,设计元器件的功能显得并不重要。 (4)对于设计中的元器件,都需要花费时间执行它的...

ic芯片设计中的静态时序分析是指对芯片电路中的时序行为进行分析和验证的过程。静态时序分析的目的是确保芯片在不同操作条件下都能按照设计要求稳定地工作。 静态时序分析的实践主要包括以下几个方面: 1. 时序约束...

静态时序分析是IC芯片设计中非常重要的一项工作,通过对时序进行分析和验证,可以保证芯片的正常运行和稳定性。以下是静态时序分析在IC芯片设计中的实践方法和步骤: 1. 收集约束信息:首先,需要收集芯片设计的...

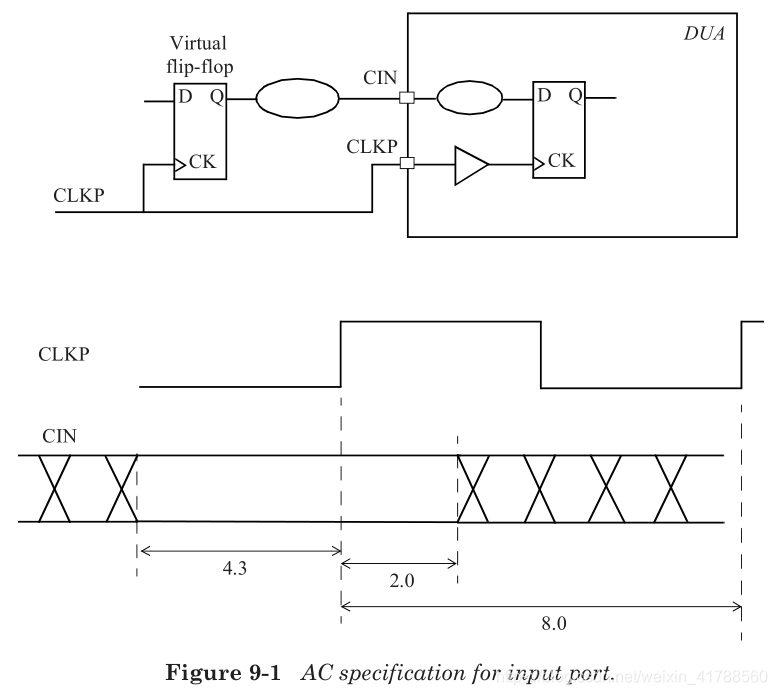

本章节将介绍静态时序分析所执行的一部分检查,这些检查旨在详尽地验证待分析设计的时序。 两项主要的检查是建立时间和保持时间检查。一旦在触发器的时钟引脚上定义了时钟,便会自动推断出该触发器的建立时间和...

数字IC笔试面试题目总结2逻辑电平静态时序分析 大部分内容均来自网络公开资料,如有侵权,请联系删除! 逻辑电平 什么是"线与"逻辑,要实现它,在硬件特性上有什么具体要求? 线与逻辑是两个输出信号相连可以实现...

静态时序分析是检查IC系统时序是否满足要求的主要手段。以往时序的验证依赖于仿真,采用仿真的方法,覆盖率跟所施加的激励有关,有些时序违例会被忽略。此外,仿真方法效率非常的低,会大大延长产品的开发周期。静态...

推荐文章

- HTML如何编写类似QQ聊天框,jQuery实现简易QQ聊天框-程序员宅基地

- 知识图谱从入门到应用——知识图谱的知识表示:符号表示方法_知识图谱符号表示-程序员宅基地

- Android Studio APK在真机上运行的方法(1)-程序员宅基地

- Unity 划线 - 使用Image实现划线_unity quest3 在image上画线-程序员宅基地

- 获取表单内部元素的N种方法_提取所有表单元素的方法-程序员宅基地

- 脑肠轴——看不见的Crosstalk_脑肠轴检测指标-程序员宅基地

- Qt安装教程(Qt 6.4)_qt6.4安装-程序员宅基地

- 解决ubuntu1604 64位安装海思V400编译器之后仍然报No such file or directory_hisilicon_v400-程序员宅基地

- 实例讲解设计模式的概念、分类、角色和交互关系 Design Patterns Elements of Reusable ObjectOriented Software-程序员宅基地

- 使用宏“CLK_OF_DECLARE” 注册clock___clk_of_table-程序员宅基地